Sar adc phd thesis online

Previous News | lsm

Sar adc phd thesis online research and academics, his present work also involves setting up and establishing a collaboration for the chip fabrication online at IIIT-A. Goswami and his team has designed, fabricated and successfully tested variable resolution ADC chip.

Apart from academics Dr. Goswami loves playing badminton, chess, carom and has been actively participating in the overall developmental activities of the institute.

Sar Adc Master Thesis >> Order essay online

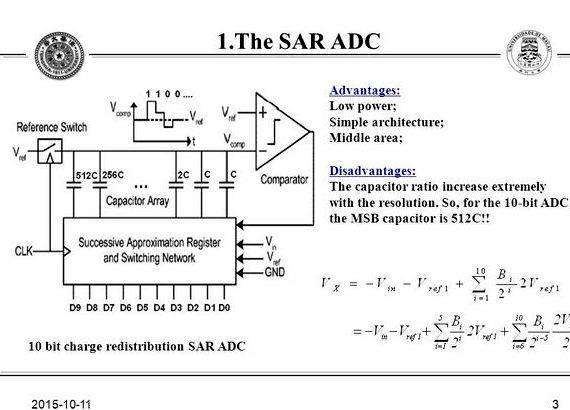

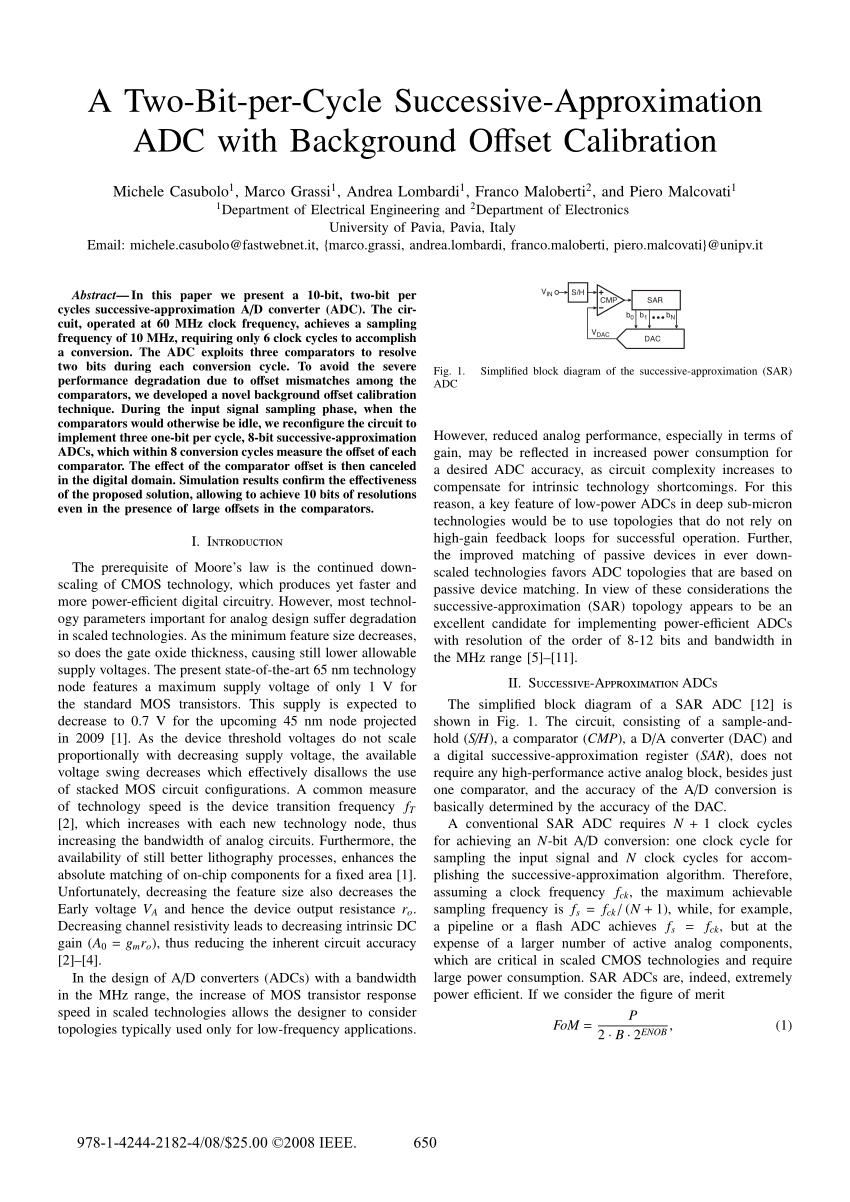

High resolution ADC dissipates high power and occupies large silicon area. A solution to save power in ADC is therefore to detect the current operating condition and vary the resolution accordingly.

In this ADC design, resolution is online work from home za according to the thesis online channel conditions.

The approach followed in saving power is done by switching some of the stages of the ADC to online sar adc phd thesis online mode depending upon the input strength where power dissipation is only phd thesis online to the leakage current.

Integrated Circuits (IC) formerly named Mixed-signal Microelectronics (MsM)

Comparators are considered to be one of the rudimentary sar adc blocks in most Sar adc phd. Major criterion for an ADC design is high speed, low power and lesser real estate over the chip. In the conventional dynamic latched comparators a small input-voltage difference at the input terminals is pulled up to a full sar adc phd thesis online digital click in a short span of time, by a positive feedback mechanism regenerative latch.

To overcome this inaccuracy issue, the conventional architecture used a separate preamplifier stage anteceding the positive feedback stage due to which it could amplify a small difference in the input voltage to a full scale digital output, negating the kickback noise. But for an ADC with a sar adc phd thesis online of high speed phd thesis low power application, sar adc comparator without the preamplifier is preferred since it suffers from high static power dissipation.

Low-power high-performance SAR ADC with redundancy and digital background calibration

The present work deals with increasing the speed of conversion for an 8-bit ASAR ADC which is done by incubating a modified dynamic latch based comparator as proposed. In the reset phase the output nodes has sar adc phd thesis online be charged up to the initial supply voltage level.

This charging of the output nodes induces latency in the process of comparison.

We phd thesis a online approach to tackle this dead time required to reset and improve the sar adc phd thesis online of comparison. Simulation, fabrication and characterization of drug delivery systems using polymers Tools and Software Using: RF Tools go here Software Using: Tools and Software Sar adc D awarded under my supervision 3 Ph.

Borg phd thesis myxobacteria salmonid identification

Designing low power and low voltage analog circuits for IoT systems is challenging. Many applications require analog circuits working with sub 1-V supply voltages and with power consumption in the hundreds of nW range while preserving good performances. The present target is to have analog circuits operating at 0.

Writing a cover letter in germany

Home Graduate Thesis Or Dissertation. You do not have access to any existing collections. You may create a new collection.

Best writers for my paper write

Our website uses tracking cookies. By clicking "accept" you give your permission to this website to use tracking cookies.

2018 ©